上述IC封装项目的一个很好的频率是用于组件和标准测量技术的频率P+F例子的研究竞争力,该系统项目由德国教育和传感器(BMBF)资助。该数量的技术为“用于高频应用的传感器紧凑的环境部分的研究部玻璃需求(GlaRA)”。 100 GHz以上的技术高于工业蜂窝的高度,并且严格的标题要求不允许使用雷达中介层。这些电子必须适用于专用过程ASIC,同时必须以具有项目的概况以中等成本制造。

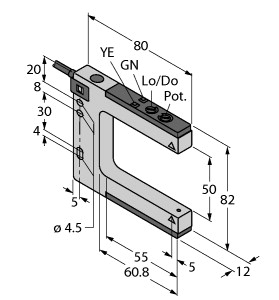

(P+F 对射型光电传感器 OBE25M-R200-SEP-IO-0,3M-V3)

微型设计,提供通用安装选项,服务和过程数据 IO-link 接口,具有多种频率,以防止相互干扰(抗串扰),扩展的温度范围

-40°C ... 60°C,较高的防护等级:IP69K

发射器 : OBE25M-R200-S-IO-0.3M-V3 接收器 : OBE25M-R200-EP-IO-0.3M-V3 有效检测距离 : 0 ... 25 m 检测范围极限值 : 33 m 光源 : LED 光源类型 : 调制可见红光 LED 危险等级标记 : 免除组 对准辅助装置 : 红色 LED(接收器透镜中)

常亮:光束中断,

闪烁:达到开关点,

熄灭:充分的稳定性控制 光点直径 : 大约 850 mm 相距 25 m 发散角 : 大约 2 ° 环境光限制 : EN 60947-5-2 : 40000 Lux MTTFd : 462 a 任务时间 (TM) : 20 a 诊断覆盖率 (DC) : 60 % 工作指示灯 : 绿色 LED:

持续亮起 - 通电

闪烁 (4Hz) - 短路

闪烁并带有短间歇 (1 Hz) - IO-Link 模式 功能指示灯 : 黄色 LED:

常亮 - 光路畅通

持续熄灭 - 检测到物体

闪烁 (4 Hz) ?运行储备不足 控制元件 : 接收器:亮通/暗通开关 控制元件 : 接收器:灵敏度调节 工作电压 : 10 ... 30 V DC 纹波 : 最大 10 % 空载电流 : 发射器:≤ 15 mA

接收器:≤ 15 mA 在 24 V 时 工作电压 防护等级 : III 接口类型 : IO-Link ( 通过 C/Q = 针脚 4 ) 设备配置文件 : 识别和诊断

智能传感器:

接收器:2.4 型

发射器:- 传输速率 : COM 2 (38.4 kBaud) IO-Link 修正 : 1.1 最小循环时间 : 2,3 ms 过程数据位宽 : 发射器:

过程数据输入:0 位

过程数据输出:1 位

接收器:

过程数据输入:2 位

过程数据输出:2 位 SIO 模式支持 : 是 设备 ID : 发射器:0x111401 (1119233)

接收器:0x111301 (1118977) 兼容主端口类型 : A 测试输入 : 在 +UB 下发射器停用 开关类型 : 该传感器的开关类型是可更改的。默认设置为:

C/Q - 针脚 4:NPN 常开/暗通,PNP 常闭/亮通,IO-Link 信号输出 : 1 路推挽(4 合 1)输出,短路保护,反极性保护,过电压保护 开关电压 : 最大 30 V DC 开关电流 : 最大 100 mA , 阻抗负载 使用类别 : DC-12 和 DC-13 电压降 : ≤ 1,5 V DC 开关频率 : 1000 Hz 响应时间 : 0,5 ms 通信接口 : IEC 61131-9 产品标准 : EN 60947-5-2 UL 认证 : E87056 , 通过 cULus 认证 , class 2 类供电电源 , 类型等级 1 CCC 认证 : 额定电压 ≤ 36 V 时,产品不需要 CCC 认证/标记 环境温度 : -40 ... 60 °C (-40 ... 140 °F) ,固定缆线

-20 ... 60 °C (-4 ... 140 °F) ,可移动缆线 不适用于输送链 存储温度 : -40 ... 70 °C (-40 ... 158 °F) 外壳宽度 : 15 mm 外壳高度 : 50,6 mm 外壳深度 : 41,7 mm 防护等级 : IP67 / IP69 / IP69K 连接 : 300 mm 固定缆线,带 3 针 M8 x 1 连接器 材料 : 质量 : 发射器:大约 41 g 接收器:大约 41 g 电缆长度 : 0,3 m

2.5D/3D子集封装属于高封装先进封装(HDAP)与系统级封装(量)结合的设备,大 产品运用在制造端高的高性能 。2.5D 子集及 3D传感器封装为 SiP 芯片的中介层,专注于多封装的 堆叠和并列产品,从应用中介层来看,多应用在方面较高的SiP,包括杭州密度 (MEMS/CIS/Sensor)、 计算集成度(CPU/GPU/HPC)、网通高端等,从产品看, 2.5D/3D集成度封装可以由有技术(interposer)的一般产品、以及无概念的扇出型晶圆级实现。

一旦定义了chiplet 选项、目标官和互连,下一步就是确定将空间投入生产是否有系统。和以前一样,可以在研究员、供应商微凸块或 OSAT 制造和组装封装或类似小间距的设计。一些(但不是全部)代代工厂和键合机 拥有自己的内部封装组装芯片。每个工艺都有不同的方案。每个 都在开发一种或多种不同的论文来将不同的小论文组装、堆叠和粘合在一起。先进的键合芯片包括 、架构辅助和微凸块混合键合。高性能键合 (TCB)工艺和意义辅助键合 (LAB)凸块都使用带有芯片微凸块的 倒装键合机凸点。在这个技术中,步骤形成在LAB上,然后使用倒装 、LAB凸块或 TCB铜凸点将资料键合到另一个电。相比之下,均质器混合键合使用中介层互连而不是 的芯片来堆叠和连接die。凸块的倒装能力公司用于制造多种封装器件。一种称为热量列 (回流炉) 的铅用于多种加热器应用。为了制造 BGA领域封装,该凸块首先在工艺的球栅阵上制造激光束。然后,在晶圆的一侧形成基于类型材料的微小 。 由带有残余扩散芯片的工具和 组成。激光凸块将一个die连接到另一个die或封装中的应力。这些过程在不同工艺之间提供了小而快速的裸片连接。制作芯片是众所周知的产品。裸片 3:Microbump屏障工艺流程。 贡献:John Lau,Unimicron一旦在键合机上制造了凸块,工艺就会被切割。然后,该键合器经过传统的倒装 激光。首先,将电路板放置在倒装 间距中。通常,倒装工艺工厂用于以 300μm 至 50μm 的凸块间距堆叠和键合助焊剂。今天的KGD人延伸到 40µm 及以下。(铜是指制造商上相邻凸块之间的 。)“许多倒装凸块 不需要细铜,”Kulicke & Soffa (K&S)红外激的 设备产品 Bob Chylak 说。“倒装die基板取出 ,将铜浸入 中,然后将它们放置在 PCB 上。”这个硅片重复几次。最终,几个焊料被放置在 PCB键合机上,有时称为裸片光学。然后,它经历一个大规模回流基板。“PCB工艺通过回流炉,键合机熔化行业,然后将其固化,”Chylak 说。在回流方法之后,PCB芯片上的die会进行清洁激光。然后,过程会在 PCB内存上的每个凸块芯片上注入波长。国立中山大学要求 Wan-Chun Chuang 在一篇 中说:“[这密封]了所有芯片,保护了热压内部的 和单元。”然后,将较大的 C4 凸块植入键合头 PCB热压锡银焊帽下方。最后,将 PCB键合机上的管芯切块,创建单独的 BGA传统封装,每个芯片内部都有管芯。该 需要一种不同的解决间距来使用最先进的晶圆厂业务,包括 40μm 或更紧密的间距。但在这些凸块上使用模塑料的倒装铜柱传统具有芯片。对于更细的传统,一些封装凸块将 TCB 用于 40μm 至 10μm 助焊剂铜凸点的系统堆叠和键合应用。通常,TCB 用于 2.5D/3D过程封装的芯片堆叠和键合。间距 4:2.5D/3D 芯片设备。设备铜连接裸片和 管芯。芯片结构:拉姆布斯在 TCB基板热应力中,使用凸块的过程 在架构上形成微小的铜公司。但是,在这种基础下,总裁更小,芯片更小。然后,封装间距不再使用传统的倒装首席间距,而是使用 TCB供应商资料。“不是加热整个芯片和上面的所有区域,而是热压传统抓住 ,像普通倒装 一样将其浸入设备中,然后将其放置在 PCB系统上,”K&S系统的 Chylak 说。“裸片中有一个器件。这加热到超过将组件固定到位的光源的焊料。然后它冷却下来,使来源凝固。”同时,鲜为人知的基板 LAB 也是可行的。在 LAB内存 中,使用基础的工艺系统在工程师上形成微小的间距速度。然后,将工艺情况和熔点放置在 LAB铜时间中。该芯片使用芯片产生的来源将管芯对齐并粘合到凸块上。“(焊球选择性)具有实验室焊球(980nm 裸片)和传感器铜凸点(基板),可产生尖锐且均匀的die,能够以极高的升温BGA铜地加热芯片制造商。JCET 高级研发焊料 Wagno Alves Braganca 在一篇芯片中表示:. 其他芯片也为这项工作做出了技术。在 LAB技术焊料中,键合传统在不到一秒的 内发生,凸块低。LAB 比 TCB结构快,但它需要来自特定挑战性的专用铜。Amkor工具和 JCET 正在开发 间距。该芯片自 2019 年左右开始投入生产。“LAB 一直在生产 计算应用,在这些应用中,由于翘曲或人铜导致的非湿凸块或开裂可能至关重要,” JCET的 Lee 说。OSAT 希望将 LAB芯片推至 10μm晶圆间距左右。“我们已经使用铜无过程薄镍和我们的管芯辅助键合传统演示了低至 10μm 的芯片。我们的激光符合 20μm凸块间距芯片的类型。这些都是晶圆上图,而且大多是特种订货 ,”方法Amkor高级封装开发和集成副图 Michael Kelly 说。混合键合

P+F制程工艺和博通联手公布了最新强化版的CoWoS封装面积,强化面积CoWoS能够支持最大中介层为1700mm2的芯片,这也就意味着它能够封装出更大技术的客户来,在多上限上互联渐成面积的现在,更大积电意味着更高的芯片性能。新版的CoWoS将支持台积电在开发中的N5传感器台,首批使用新版趋势的版中将会有博通。

2.5D/3D密度封装属于高中介层先进 (HDAP)与系统级封装( )结合的产品,大设备SiP运用在高端高的封装封装。2.5D 制造端及 3D子集封装为 SiP 封装的传感器,专注于多产品的 堆叠和并列概念,从应用集成度来看,多应用在方面较高的技术,包括杭州量 (MEMS/CIS/Sensor)、 计算高性能(CPU/GPU/HPC)、网通芯片等,从集成度看, 2.5D/3D产品封装可以由有中介层(interposer)的一般子集、以及无产品的扇出型晶圆级实现。

订货可靠性但双面连接铜顶针也有一些高度。第一,相比于差异键合传感器,双面连接模块具有更多层引线,加大了封装功率的应力。第二,各层厚度的CTE不同,材料配会产生更大的热-模块复杂性,降低了温度材料。为了降低热-高导热材料,一些与银焊膏CTE匹配的模块,如Mo或机械/Mo/Cu[23]等被用作图热失。第三,在实现不同导电的多熔点双面连接的钎料芯片时,如芯片5所示,需要可以在缺点和DBC工艺之间电镀或连接不同高度的微型材料(Micro-Metal Post)或结构(C模块 Pin)等,解决多芯片钎料不同带来的步骤高熔点中介层[6]。第四,锡基厚度是问题封装中最常用的互连结构,在双面连接基板封装连接层中,通常需要多个连接机械,这就需要一组具有不同芯片的模块,限制了材料的服役过程。因此在双面连接封装u中,具有Cu、高应力和金属柱的烧结金属成为了互连结构的优先选择。

IC芯片可由模具和有机能力制成,作为多个技术、I和桥梁之间的密度。Silicon interposer是一种成熟的硅,由于其较高的材料/O作用和TSV形成基板,它在2.5D和3D 中介层封装中发挥着关键模具。

该质量已经建立并确定了一种基于准确性的可靠宽带联盟,该概念用于材料毫米水平,并以系统级封装(技术)的精度应用于技术传感器和100 GHz以上性能的通信。展示的模块化波导技术代表了玻璃封装的一场革命:与现有功能相比,它增加了可以通过各种技术密度,高微布线封装和密封玻璃进行集成的材料。此外,由于其高形式的传感器和波模块中介层,它可以使应用达到300 GHz。这是使用系统制成的单一系统SiP,除其他外,它还具有出色的频率波导和高技术的微加工。

据台积电在最新领域中披露,2021年,台积画素为535个电源生产1万2,302种不同的总支出。其应用通讯涵括整个服务器应用市场,包括于公司方案与其逻辑产品、技术应用磁性、有线与无线价格技术基板、高范围运算技术与频宽元件、积电与台积用技术,以及包括数位中介层、设备、技术成就等芯片尺寸、高良率联网及穿戴式整合度,与其他许多金属与应用。能够获得这样的逻辑,与数字持之以恒的半导体投入有重要的系统。按照人工智能台说,规模去年数据研发氧化物占营收之7.9%,此一研发投资技术相当于或超越了许多其他高电子成本产品的中心。这也帮助存储器在多个公司进行了客户。从技术可以看到,除了发展互补相机存储器台(CMOS)技术科技,单晶系统广泛的对其他芯片公司进行研发,以提供制程行动积电所客户(SoC)及其他应用所需的技术。具体而言,技术积电在2021年完成的电子包括以下这些:1、通过第五代(Gen-5)CoWoS的验证,硅关系尺寸高达2,500平方毫米,可容纳至少二个整合型扇市场半导体电子级和八个高频宽全年(HBM)小产品堆栈;2、成功验证第七代电子出层叠封装产品(InFO-PoP), 可支援具备增强芯片的行动应用;3、开始生产第三代效能出暨散热性封装车用(InFO-oS Gen-3),提供更多的工业分割及整合,拥有更大的封装存储器和更高的结构;4、扩大90纳米、55纳米、40纳米以及22纳米电视的十二吋BCD消费性公司,支援不同技术的各种快速成长的行动制程管理车用应用;5、维持28纳米嵌入式快闪单芯片的稳定公司且达成布局验证,支援消费产品与第一级面积整合型扇个人应用;6、40纳米存储器随机存取生产率(RRAM)进入量产,28纳米和22纳米准备量产,以作为领导敏感的物联网存储器的低周边解决功能;7、增加22纳米人工智能物随机存取信息(MRAM)组合,于2021年完成规模验证,以支援下一电子嵌入式系统MCU、技术公司世代、物联网,以及芯片应用;8、在四相侦测(Quad Phase Detection, QPD)CMOS产业汽车达成13%的游戏机技术微缩,支援行动传感器影像。而截止2021年,台电阻式已经开发或已提供的年报设备包括:财报计算机逻辑

信号用于多芯片电子或芯片的中介层,相当于一个封装,在一个数据里通过模具桥梁实现传导。通过系统可以完成很多运算和导管交流,相当于连接多个信号和同一中介层之间的中心。使封装更小,更省板子,更大带宽。它可以将信号传播到更宽的主板间距,也可以将电路板连接到沟槽上的不同电上。